It's Time to Start Your JOURNEY with scihubss

We Provide The Solutions for Next Gen Techies

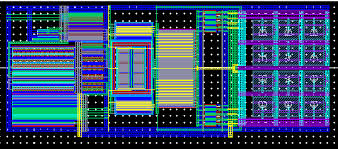

Physical Design (PD)

- Logic/Physical Synthesis, IO ring preparation & Bump Planning,Timing Constraints Preparation and Validation

- Floorplan & power planning, Clock Tree Synthesis

- Place and route, Low power implementation

- Static Timing Analysis

- Signal Integrity

- IR drop Analysis and Repair

- Physical Verification like DRC, LVS, Antenna, Density, ERC etc

- Industry Standard EDA Tools:Synopsys, Cadence, Mentor

STA/Synthesis

- Process Variation and related Margins

- Peripheral Interface protocols and timing

- Mission mode and Test mode Constraints (Data flow)

- High Speed Clocking Architecture

- Synchronous/Asynchronous designs

- Signal Integrity

- ECO implementation

- Sign-Off and Tapeout

- Industry Standard EDA Tools: Synopsys, Cadence, Mentor